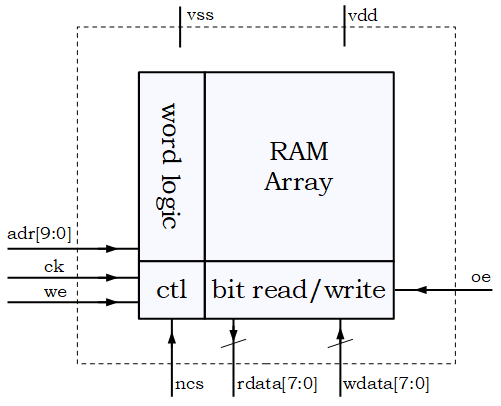

Low cost, small RAM’s in standard design rules supplied in 1Kb, 4Kb, and 16Kb fixed block sizes.

Uses only 1.8V core fet components and in compaible with most TSMC 180n processes.

Features

- 8b, 16b, and 32b data widths available.

- Up to 250MHz clock operation.

- Read and write data busses may tie for single bus operation.

- Available production test RTL.

- VDD 1.6V – 2.0V.

- Data retention to 0.9V.

- Temperature range -40C to 125C.

- Chip select and output enable controls for simple parallel operation.

Typical Applications

- Low cost embedded RAM.

- High speed MPU RAM.

Deliverables

- Verilog Model.

- Timing .lib timing files.

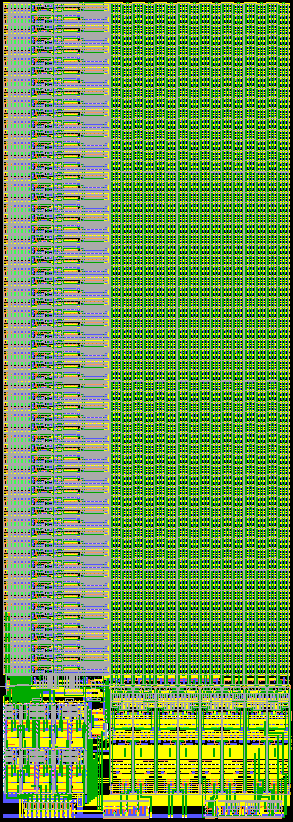

- GDS Layout.

- LEF.

- LVS netlist.

- DRC/LVS results.

- Integration notes.

- Production test notes.