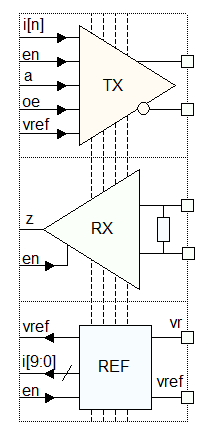

OT3910bj is a set of cells designed for implementing the transmitter, receiver and associated bias function for LVDS point to point communication on the ams aH18 process. Compatible power pads are also provided.

The transmit driver cell translates 1.8V core logic signal levels to LVDS levels with a typical differential output swing of 350mV. The receiver cell translates LVDS levels, with a typical differential input threshold of of above 100mV, to 1.8V core logic signal levels. A reference cell is also provided to produce appropriate bias currents voltage reference signals for the transmit and receive cells.

Features

- Meets or exceeds the TIA/EIA-644 LVDS standard.

- Driver, Receiver, Bias, and Power cells included.

- Greater than 400Mbs data rate.

- 1.8V core voltage, 5V IO voltage.

- Receive fault detection.

- 0.3ns differential pulse skew.

- 1ns receive propagation delay.

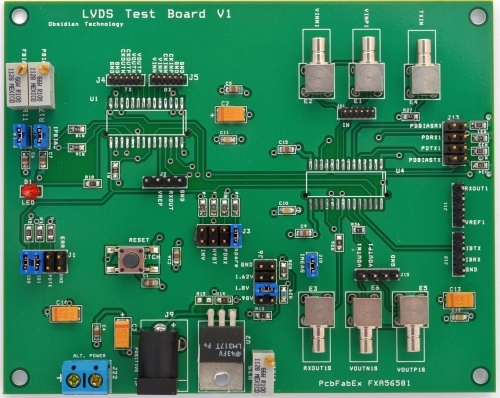

- Available evaluation chip, and evaluation board.

Standard Deliverables

- Flat GDS layout (for some IP this is delivered to the fab for integration).

- Verilog model.

- SPICE/CDL netlist.

- Basic SPICE testbench. Allows for verification of basic function.

- Timing files in LIB format.

- Optional test chips.

- Integration notes, and integration consulting support.

- Test implementation notes.