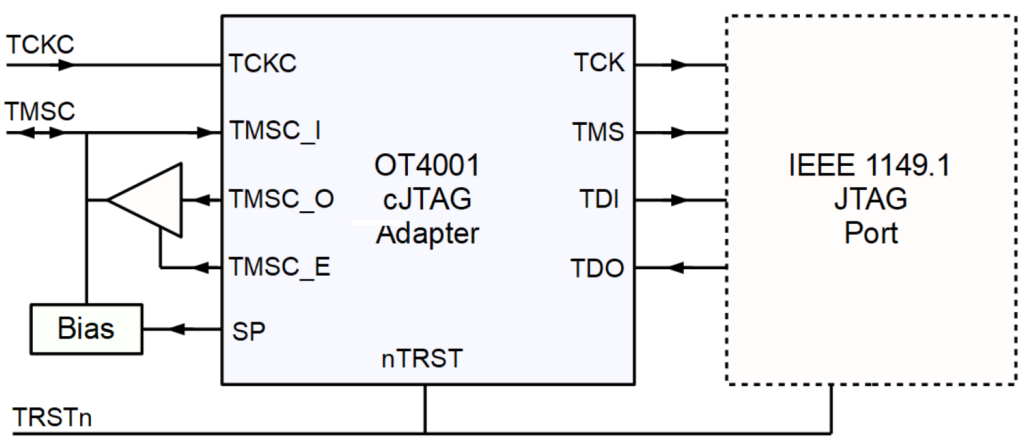

The OT4001_cjtag is an adapter which permits legacy IEEE 1149.1 ports to communicate as an IEEE 1149.7 2-wire OScan1 cJTAG port. A simple update to a 1149.1 port to support 1149.7 2-wire signaling. This can be used for reduction in pin count for chips with JTAG interfaces. The IP is in the form of synthesizable verilog. May be implemented in ASIC or FPGA.

Features

- IEEE 1149.1 and IEEE 1147.7 compatible.

- Small logic overhead.

- Clock frequencies to 25MHz.

- Activated with a 12b Online Activation Code.

- Available setup support code for Digilent SDK and OpenOCD.

- Available CPLD for test system debug prior to silicon.

- Delivered as obfuscated verilig.

Pricing is $8K for a muli-use license. Contact info@ot1.com for further information.